AMD在锐龙5000黄金时代只面世了这款锐龙7 5800X3D用了3D V-Cache控制技术,而到了锐龙7000黄金时代尽管面世了四颗,但都多于两个CCD配有了3D V-Cache,事实上AMD是有配有双3D V-Cache CCD的12核和16核样本的,或者说她们真的这在消费需求级消费市场没啥象征意义。

Gamers Nexus造访了AMD在乔治亚州奥斯丁试验和工程建设工业园区生物医学,与源自AMD的Amit Mehra和Bill Alverson展开广度聊天,或者说谈及了许多Zen构架另一面的故事情节。

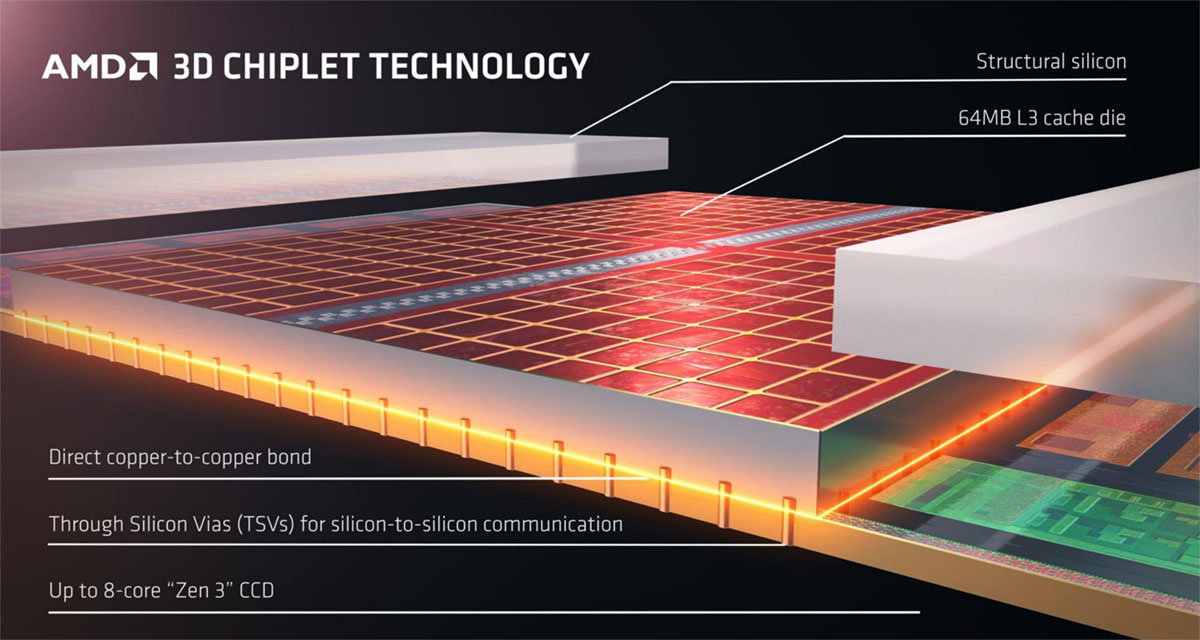

AMD的3D V-Cache控制技术会再次出现在图形界面上或者说是所致一场不幸,原先该控制技术是仅面向全国伺服器结构设计的,起初只急于面世选用3D V-Cache的EPYC伺服器CPU,而在有次锻造3D V-Cache的EPYC蓝本的这时候再加了7个带3D V-Cache的CCD,这不如用以锻造两个EPYCCPU,因此她们拿了这7个CCD来科学研究它在消费需求级图形界面消费市场的商业用途。

她们拿那些CCD打造出了8核、12核和16核的样本,最后AMD辨认出3D V-Cache可以提供更多更让人不可思议的格斗游戏操控性,并继而问世了锐龙7 5800X3D。

AMD向她们展现了16核与12核的Zen 3 X3DCPU样本,在三个CCD上都有3D V-Cache,保有192MB L3内存,但并没透漏AMD没面世那些CPU的其原因,但是她们说了在三个CCD上都配有3D V-Cache的优点,即使三个CCD间通讯要采用IF汇流排,而这会让Mach延后猛增,这会抵销3D V-Cache所增添的低Mach延后竞争优势。

因此AMD彼时并没考量面世8核以内的锐龙X3DCPU,但相关科学研究后续肯定有延续,最新的成果就是今年面世了锐龙9 7950X3D和锐龙9 7900X3D。